Please provide all those.

Seems everything is fine.

| Line 330: [ 0.431159] ep_pcie_core_enable_endpoint: PCIe : quectel_01 pcie subsystem set id 520117cb | |

|---|---|

| Line 331: [ 0.431177] ep_pcie_reset_init: After Reset assert pcie_core_reset | |

| Line 332: [ 0.432212] ep_pcie_reset_init: After Reset de-assert pcie_core_reset | |

| Line 333: [ 0.432223] ep_pcie_reset_init: After Reset assert pcie_phy_reset | |

| Line 334: [ 0.433247] ep_pcie_reset_init: After Reset de-assert pcie_phy_reset | |

| Line 335: [ 0.433257] ep_pcie_core_enable_endpoint: PCIe V1711211: assert PCIe WAKE# | |

| Line 336: [ 0.435385] ep_pcie_core_enable_endpoint: PCIe V1711211: PCIe PHY is ready | |

| Line 337: [ 0.435432] ep_pcie_core_init: PCIe : quectel pcie subsystem id is 520117cb | |

| Line 338: [ 0.435462] ep_pcie_core_init: PCIe : LGW pcie earlier set BHI_EXECENV register AMSS state [2] | |

| Line 339: [ 0.450626] ep_pcie_core_enable_endpoint: PCIe V1711211: link initialized for LE PCIe endpoint | |

| Line 340: [ 0.450649] ep_pcie_enumeration: PCIe V1711211: PCIe link training is successful with host side. Waiting for enumeration to complete |

Hi Bean,

Please find the attached logs ,

HOST SIDE

proto_lspci-vvv.txt (56.6 KB)

proto_lspci-v.txt (10.0 KB)

proto_lspci.txt (600 Bytes)

proto_dmesg.txt (6.3 KB)

host_cat_logs.txt (4.5 KB)

MODEM SIDE

proto_modem_uart_logs.txt (17.9 KB)

modem_dmesg_logs.txt (87.9 KB)

modem_cat_logs.txt (250.1 KB)

Hi Bean,

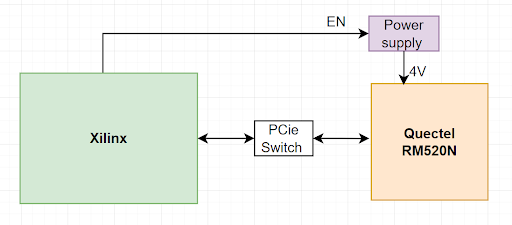

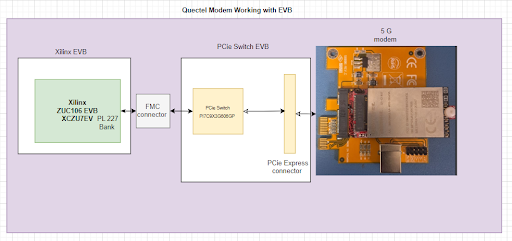

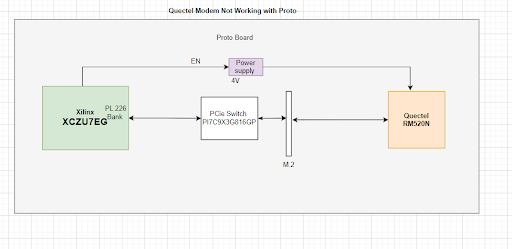

We have one Xilinx zynq MPSoC evaluation kit with another PCIE switch with four modems is working fine

Now we are using our own custom board, same modem we are connecting its not working

modem state PCIe register

root@SD:~# devmem 0xa0000038

0x00000200

root@SD:~# devmem 0xa0000048

0x00000101

this address not getting updated but in working conditions its value will be 201

Do you know the firmware version of the modem?

Hi Bean,

Is any way to find it?

How and when do you power on the RM520NGL?

Does the RM520N power on at the same time with Xlinx?

Is there any PCIe driver in the bootloader of the Xlinux?

Is there any difference between the two Xlinx board?

I have checked.

Some other Quectel customer have also such problems.

The Xlinx vendor modified the configuration of the PS side and confirmed that there was a problem with the communication between the PS and the PL, causing the PS not to respond to the request from the PL.

Hi Bean,

Does the RM520N power on at the same time with Xlinx? Here xilinx and modem powering up same time

There is no pcie mhi driver in linux 5.10 from xilinx.I have attached power up sequence,

Hi Bean,

From the below logs we can able to get the firmware version

RDY

+CFUN: 1

+CPIN: READY

+QUSIM: 1

+QIND: SMS DONE

+QIND: PB DONE

ATI

Quectel

RM520N-GL

Revision: RM520NGLAAR01A08M4G

OK

AT+GMR

RM520NGLAAR01A08M4G

OK

Same kernel source code?

Quectel think it is better to check with the vendor of the Xlinx.

There might be something wrong with the MSI interrups.

Hi Bean ,

Yes same quectel source code we are using for that board

Hi Bean,

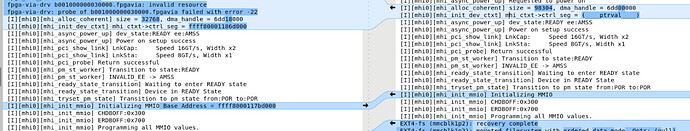

Working scenario of xilinx evaluation board,

Non working state of our proto board,

At least we could make the RM520N PCIE is fine.

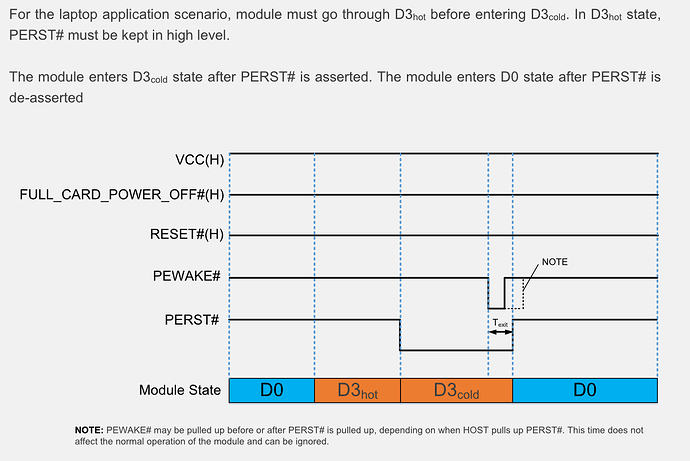

My suspicion is that the boot sequence is not satisfied. So it is better to check the waveform of the PCIE_RST and PCIE_WAKE.

From the picture, maybe the time RM520N power one is not the same.

Quetel software RD think it is better to ask the Xlinx.

There is another customer have try PCIE modem on Xlinux.

The Xlinx vendor modified the configuration of the PS side and confirmed that there was a problem with the communication between the PS and the PL, causing the PS not to respond to the request from the PL.

So please compare the source code.

Hi Bean,

Can we read or access controller-level registers other than the PCIE domain? Just to make sure that controller is up or not

We know that PCIE domain is working and able to access the registers, we are not sure if the controller level is up or not

is there any way we can get register map sheet?

No.

We could access the PCIE EP device with memory map could not provide the registers map.

Hi Bean,

We compared working logs and non-working logs

from the image in working log mhi_ctrl->ctrl_reg = ffff80001186d00 and

Intializing MMIO Base Address = ffff80001186d00

but in not working we are receiving anything.

Could you please check on this?

Hi Bean,

Thanks for the support. It started working we missed some pins mapping to modem.

Great to hear that you have solved it!