Hi @silvia ,

I have an RM502Q-GL with this firmware RM502QGLAAR11A02M4G_01.200.01.200, and I’m trying to make it working on PCIe bus (instead of USB), but no way.

There are the commands that I’m sending on AT port:

AT+QCFG=“data_interface”,1,0

Pinging the module says that all is set, but when attach it to PCIe bus, there is no device detected

AT+QCFG=“data_interface”

OK

Is a firmware bug or module issue? Let me know if you need other logs.

Thanks!

silvia

August 8, 2025, 3:37am

2

Dear @stich86

Yes did all the steps (rebooted all the times), but it doesn’t appear on lspci

Looks like it doesn’t switch or enable PCIe lanes

hi @silvia ,

any update? I’ve seen in the hw desing that there are three different variatns of RM520Q-GL.

How to check if there are some eFuse or something else that block PCIe mode?

Thanks

silvia

August 20, 2025, 6:53am

5

Dear @stich86

I’m currently on holidays, i’ll try again next week and le you known.

Any others check that I can do (logs or something else) to understand if it’s not supported?

Thanks!

silvia

August 21, 2025, 3:57am

7

Dear @stich86

Hi silvia,

so I’ve double checked:

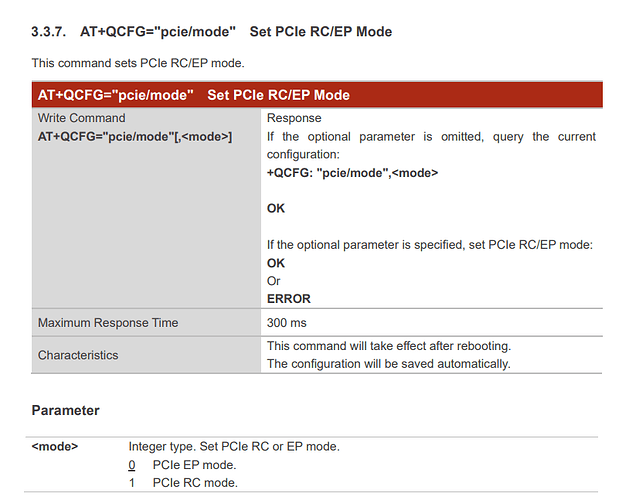

pcie_mode is 0 (EP)

Anyway, when CPE boots it doesn’t find the module on PCIe bus:

[ 0.098204] mtk-pcie-gen3 11280000.pcie: host bridge /soc/pcie@11280000 ranges:

[ 0.098222] mtk-pcie-gen3 11280000.pcie: Parsing ranges property...

[ 0.098234] mtk-pcie-gen3 11280000.pcie: MEM 0x0020000000..0x002fffffff -> 0x0020000000

[ 2.303272] mtk-pcie-gen3 11280000.pcie: host bridge /soc/pcie@11280000 ranges:

[ 2.310632] mtk-pcie-gen3 11280000.pcie: Parsing ranges property...

[ 2.316900] mtk-pcie-gen3 11280000.pcie: MEM 0x0020000000..0x002fffffff -> 0x0020000000

[ 2.325540] mtk-pcie-gen3 11280000.pcie: failed to get max link width

[ 2.669022] mtk-pcie-gen3 11280000.pcie: PCIe link down, current LTSSM state: detect.quiet (0x1)

[ 2.677844] mtk-pcie-gen3: probe of 11280000.pcie failed with error -110

[ 11.439375] mhi_init Quectel_Linux_PCIE_MHI_Driver_V1.3.8

On the same board, an RM520GLAP is recognized:

[ 2.303498] mtk-pcie-gen3 11280000.pcie: host bridge /soc/pcie@11280000 ranges:

[ 2.310878] mtk-pcie-gen3 11280000.pcie: Parsing ranges property...

[ 2.317149] mtk-pcie-gen3 11280000.pcie: MEM 0x0020000000..0x002fffffff -> 0x0020000000

[ 2.325794] mtk-pcie-gen3 11280000.pcie: failed to get max link width

[ 2.586952] mtk-pcie-gen3 11280000.pcie: set MEM trans window[0]: cpu_addr = 0x20000000, pci_addr = 0x20000000, size = 0x10000000

[ 2.598792] mtk-pcie-gen3 11280000.pcie: PCI host bridge to bus 0001:00

[ 2.605416] pci_bus 0001:00: root bus resource [bus 00-ff]

[ 2.610899] pci_bus 0001:00: root bus resource [mem 0x20000000-0x2fffffff]

[ 2.617761] pci_bus 0001:00: scanning bus

[ 2.621788] pci 0001:00:00.0: [14c3:1f32] type 01 class 0x060400

[ 2.627795] pci 0001:00:00.0: reg 0x10: [mem 0x00000000-0x00007fff 64bit]

[ 2.634638] pci 0001:00:00.0: PME# supported from D0 D3hot D3cold

[ 2.640727] pci 0001:00:00.0: PME# disabled

[ 2.646010] pci_bus 0001:00: fixups for bus

[ 2.650213] pci 0001:00:00.0: scanning [bus 00-00] behind bridge, pass 0

[ 2.656903] pci 0001:00:00.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 2.664905] pci 0001:00:00.0: scanning [bus 00-00] behind bridge, pass 1

[ 2.671691] pci_bus 0001:01: scanning bus

[ 2.675725] pci 0001:01:00.0: [17cb:0308] type 00 class 0xff0000

[ 2.681759] pci 0001:01:00.0: reg 0x10: [mem 0x00000000-0x00000fff 64bit]

[ 2.688551] pci 0001:01:00.0: reg 0x18: [mem 0x00000000-0x00000fff 64bit]

[ 2.695489] pci 0001:01:00.0: PME# supported from D0 D3hot D3cold

[ 2.701580] pci 0001:01:00.0: PME# disabled

[ 2.705797] pci 0001:01:00.0: 4.000 Gb/s available PCIe bandwidth, limited by 5.0 GT/s PCIe x1 link at 0001:00:00.0 (capable of 15.752 Gb/s with 8.0 GT/s PCIe x2 link)

[ 2.749104] pci_bus 0001:01: fixups for bus

[ 2.753286] pci_bus 0001:01: bus scan returning with max=01

[ 2.758845] pci_bus 0001:01: busn_res: [bus 01-ff] end is updated to 01

[ 2.765467] pci_bus 0001:00: bus scan returning with max=01

[ 2.771060] pci 0001:00:00.0: BAR 8: assigned [mem 0x20000000-0x200fffff]

[ 2.777838] pci 0001:00:00.0: BAR 0: assigned [mem 0x20100000-0x20107fff 64bit]

[ 2.785150] pci 0001:01:00.0: BAR 0: assigned [mem 0x20000000-0x20000fff 64bit]

[ 2.792467] pci 0001:01:00.0: BAR 2: assigned [mem 0x20001000-0x20001fff 64bit]

[ 2.799780] pci 0001:00:00.0: PCI bridge to [bus 01]

[ 2.804735] pci 0001:00:00.0: bridge window [mem 0x20000000-0x200fffff]

[ 2.811643] pcieport 0001:00:00.0: assign IRQ: got 85

[ 2.816688] pcieport 0001:00:00.0: enabling device (0000 -> 0002)

[ 2.822787] pcieport 0001:00:00.0: enabling bus mastering

[ 2.828782] mtk-pcie-gen3 11280000.pcie: msi#0x0 address_hi 0x0 address_lo 0x11280c00 data 0

[ 2.837227] mtk-pcie-gen3 11280000.pcie: msi#0x1 address_hi 0x0 address_lo 0x11280c00 data 1

[ 2.845659] mtk-pcie-gen3 11280000.pcie: msi#0x2 address_hi 0x0 address_lo 0x11280c00 data 2

[ 2.854089] mtk-pcie-gen3 11280000.pcie: msi#0x3 address_hi 0x0 address_lo 0x11280c00 data 3

[ 2.862519] mtk-pcie-gen3 11280000.pcie: msi#0x4 address_hi 0x0 address_lo 0x11280c00 data 4

[ 2.870953] mtk-pcie-gen3 11280000.pcie: msi#0x5 address_hi 0x0 address_lo 0x11280c00 data 5

[ 2.879383] mtk-pcie-gen3 11280000.pcie: msi#0x6 address_hi 0x0 address_lo 0x11280c00 data 6

[ 2.887807] mtk-pcie-gen3 11280000.pcie: msi#0x7 address_hi 0x0 address_lo 0x11280c00 data 7

[ 2.896237] mtk-pcie-gen3 11280000.pcie: msi#0x8 address_hi 0x0 address_lo 0x11280c00 data 8

[ 2.904669] mtk-pcie-gen3 11280000.pcie: msi#0x9 address_hi 0x0 address_lo 0x11280c00 data 9

[ 2.913099] mtk-pcie-gen3 11280000.pcie: msi#0xa address_hi 0x0 address_lo 0x11280c00 data 10

[ 2.921615] mtk-pcie-gen3 11280000.pcie: msi#0xb address_hi 0x0 address_lo 0x11280c00 data 11

[ 2.930134] mtk-pcie-gen3 11280000.pcie: msi#0xc address_hi 0x0 address_lo 0x11280c00 data 12

[ 2.938645] mtk-pcie-gen3 11280000.pcie: msi#0xd address_hi 0x0 address_lo 0x11280c00 data 13

[ 2.947161] mtk-pcie-gen3 11280000.pcie: msi#0xe address_hi 0x0 address_lo 0x11280c00 data 14

[ 2.955678] mtk-pcie-gen3 11280000.pcie: msi#0xf address_hi 0x0 address_lo 0x11280c00 data 15

[ 2.964194] mtk-pcie-gen3 11280000.pcie: msi#0x10 address_hi 0x0 address_lo 0x11280c00 data 16

[ 2.972797] mtk-pcie-gen3 11280000.pcie: msi#0x11 address_hi 0x0 address_lo 0x11280c00 data 17

[ 2.981400] mtk-pcie-gen3 11280000.pcie: msi#0x12 address_hi 0x0 address_lo 0x11280c00 data 18

[ 2.990006] mtk-pcie-gen3 11280000.pcie: msi#0x13 address_hi 0x0 address_lo 0x11280c00 data 19

[ 2.998603] mtk-pcie-gen3 11280000.pcie: msi#0x14 address_hi 0x0 address_lo 0x11280c00 data 20

[ 3.007206] mtk-pcie-gen3 11280000.pcie: msi#0x15 address_hi 0x0 address_lo 0x11280c00 data 21

[ 3.015811] mtk-pcie-gen3 11280000.pcie: msi#0x16 address_hi 0x0 address_lo 0x11280c00 data 22

[ 3.024414] mtk-pcie-gen3 11280000.pcie: msi#0x17 address_hi 0x0 address_lo 0x11280c00 data 23

[ 3.033017] mtk-pcie-gen3 11280000.pcie: msi#0x18 address_hi 0x0 address_lo 0x11280c00 data 24

[ 3.041620] mtk-pcie-gen3 11280000.pcie: msi#0x19 address_hi 0x0 address_lo 0x11280c00 data 25

[ 3.050236] mtk-pcie-gen3 11280000.pcie: msi#0x1a address_hi 0x0 address_lo 0x11280c00 data 26

[ 3.058834] mtk-pcie-gen3 11280000.pcie: msi#0x1b address_hi 0x0 address_lo 0x11280c00 data 27

[ 3.067437] mtk-pcie-gen3 11280000.pcie: msi#0x1c address_hi 0x0 address_lo 0x11280c00 data 28

[ 3.076041] mtk-pcie-gen3 11280000.pcie: msi#0x1d address_hi 0x0 address_lo 0x11280c00 data 29

[ 3.084644] mtk-pcie-gen3 11280000.pcie: msi#0x1e address_hi 0x0 address_lo 0x11280c00 data 30

[ 3.093246] mtk-pcie-gen3 11280000.pcie: msi#0x1f address_hi 0x0 address_lo 0x11280c00 data 31

[ 3.102600] mtk-pcie-gen3 11280000.pcie: msi#0x0 address_hi 0x0 address_lo 0x11280c00 data 0

[ 3.111184] pcieport 0001:00:00.0: PME: Signaling with IRQ 86

[ 3.117235] pcieport 0001:00:00.0: AER: enabled with IRQ 86

[ 3.122947] pcieport 0001:00:00.0: save config 0x00: 0x1f3214c3

[ 3.128861] pcieport 0001:00:00.0: save config 0x04: 0x00100406

[ 3.134785] pcieport 0001:00:00.0: save config 0x08: 0x06040001

[ 3.140704] pcieport 0001:00:00.0: save config 0x0c: 0x00010000

[ 3.146611] pcieport 0001:00:00.0: save config 0x10: 0x20100004

[ 3.152525] pcieport 0001:00:00.0: save config 0x14: 0x00000000

[ 3.158432] pcieport 0001:00:00.0: save config 0x18: 0x00010100

[ 3.164345] pcieport 0001:00:00.0: save config 0x1c: 0x000001f1

[ 3.170256] pcieport 0001:00:00.0: save config 0x20: 0x20002000

[ 3.176163] pcieport 0001:00:00.0: save config 0x24: 0x0001fff1

[ 3.182075] pcieport 0001:00:00.0: save config 0x28: 0x00000000

[ 3.187982] pcieport 0001:00:00.0: save config 0x2c: 0x00000000

[ 3.193893] pcieport 0001:00:00.0: save config 0x30: 0x00000000

[ 3.199809] pcieport 0001:00:00.0: save config 0x34: 0x00000080

[ 3.205717] pcieport 0001:00:00.0: save config 0x38: 0x00000000

[ 3.211629] pcieport 0001:00:00.0: save config 0x3c: 0x00020155

[ 12.087300] mhi_init Quectel_Linux_PCIE_MHI_Driver_V1.3.8

[ 12.093077] mhi_q 0001:01:00.0: assign IRQ: got 0

[ 12.097812] mhi_pci_probe pci_dev->name = 0001:01:00.0, domain=1, bus=1, slot=0, vendor=17CB, device=0308

[ 12.107598] [I][mhi0][mhi_arch_set_bus_request] Setting bus request to index 1

[ 12.114851] mhi_q 0001:01:00.0: BAR 0: assigned [mem 0x20000000-0x20000fff 64bit]

[ 12.122404] mhi_q 0001:01:00.0: enabling device (0000 -> 0002)

[ 12.128246] mhi_q 0001:01:00.0: enabling bus mastering

[ 12.133544] mtk-pcie-gen3 11280000.pcie: msi#0x4 address_hi 0x0 address_lo 0x11280c00 data 4

[ 12.142191] mtk-pcie-gen3 11280000.pcie: msi#0x5 address_hi 0x0 address_lo 0x11280c00 data 5

[ 12.150652] mtk-pcie-gen3 11280000.pcie: msi#0x6 address_hi 0x0 address_lo 0x11280c00 data 6

[ 12.159089] mtk-pcie-gen3 11280000.pcie: msi#0x7 address_hi 0x0 address_lo 0x11280c00 data 7

[ 12.167743] [I][mhi0][mhi_init_pci_dev] msi_required = 4, msi_allocated = 4, msi_irq = 91

[ 12.176111] [I][mhi0][mhi_power_up] dev_state:READY

[ 12.180992] [I][mhi0][mhi_async_power_up] Requested to power on

[ 12.187137] [I][mhi0][mhi_alloc_coherent] size = 98304, dma_handle = 44500000

[ 12.194266] [I][mhi0][mhi_init_dev_ctxt] mhi_ctxt->ctrl_seg = 000000001c8efecb

[ 12.202220] [I][mhi0][mhi_async_power_up] dev_state:READY ee:AMSS

[ 12.208351] [I][mhi0][mhi_async_power_up] Power on setup success

[ 12.214608] [I][mhi0][mhi_pci_show_link] LnkCap: Speed 8GT/s, Width x2

[ 12.221167] [I][mhi0][mhi_pci_show_link] LnkSta: Speed 5GT/s, Width x1

[ 12.227689] [I][mhi0][mhi_pci_probe] Return successful

[ 12.233015] [I][mhi0][mhi_pm_st_worker] Transition to state:READY

[ 12.239326] [I][mhi0][mhi_pm_st_worker] INVALID_EE -> AMSS

[ 12.244807] [I][mhi0][mhi_ready_state_transition] Waiting to enter READY state

[ 12.252233] [I][mhi0][mhi_ready_state_transition] Device in READY State

[ 12.252591] usbcore: registered new interface driver cdc_ether

[ 12.258841] [I][mhi0][mhi_tryset_pm_state] Transition to pm state from:POR to:POR

[ 12.272136] [I][mhi0][mhi_init_mmio] Initializing MMIO

[ 12.272605] usbcore: registered new interface driver cdc_ncm

[ 12.277455] [I][mhi0][mhi_init_mmio] CHDBOFF:0x300

[ 12.287898] [I][mhi0][mhi_init_mmio] ERDBOFF:0x700

[ 12.292693] [I][mhi0][mhi_init_mmio] Programming all MMIO values.

[ 12.389255] [I][mhi0][mhi_dump_tre] carl_ev evt_state_change mhistate=2

[ 12.395889] [I][mhi0][mhi_process_ctrl_ev_ring] MHI state change event to state:M0

[ 12.403483] [I][mhi0][mhi_pm_m0_transition] Entered With State:READY PM_STATE:POR

[ 12.410982] [I][mhi0][mhi_tryset_pm_state] Transition to pm state from:POR to:M0

[ 12.418422] [I][mhi0][mhi_dump_tre] carl_ev evt_ee_state execenv=2

[ 12.424618] [I][mhi0][mhi_process_ctrl_ev_ring] MHI EE received event:AMSS

[ 12.432047] [I][mhi0][mhi_pm_st_worker] Transition to state:MISSION MODE

[ 12.438953] [I][mhi0][mhi_pm_st_worker] INVALID_EE -> AMSS

[ 12.444487] [I][mhi0][mhi_pm_mission_mode_transition] Processing Mission Mode Transition

[ 12.452819] [I][mhi0][mhi_init_timesync] TIME OFFS:0xa20

[ 12.458354] [I][mhi0][mhi_pm_mission_mode_transition] Adding new devices

[ 12.467624] [I][mhi0][mhi_dtr_probe] Enter for DTR control channel

[ 12.473829] [I][mhi0][__mhi_prepare_channel] Entered: preparing channel:18

[ 12.484817] [I][mhi0][mhi_dump_tre] carl_ev evt_cmd_comp code=1, type=33

[ 12.519094] [I][mhi0][__mhi_prepare_channel] Chan:18 successfully moved to start state

[ 12.527025] [I][mhi0][__mhi_prepare_channel] Entered: preparing channel:19

[ 12.538058] [I][mhi0][mhi_dump_tre] carl_ev evt_cmd_comp code=1, type=33

[ 12.546301] usbcore: registered new interface driver qmi_wwan

[ 12.552190] [I][mhi0][__mhi_prepare_channel] Chan:19 successfully moved to start state

[ 12.560372] [I][mhi0][mhi_dtr_probe] Exit with ret:0

[ 12.565879] [I][mhi_netdev_enable_iface] Prepare the channels for transfer

[ 12.572781] [I][mhi0][__mhi_prepare_channel] Entered: preparing channel:100

[ 12.583896] usbcore: registered new interface driver usbserial_generic

[ 12.587796] [I][mhi0][mhi_dump_tre] carl_ev evt_cmd_comp code=1, type=33

[ 12.590513] usbserial: USB Serial support registered for generic

[ 12.597387] [I][mhi0][__mhi_prepare_channel] Chan:100 successfully moved to start state

[ 12.611155] [I][mhi0][__mhi_prepare_channel] Entered: preparing channel:101

any other check that I can do?

Thanks!

silvia

August 25, 2025, 6:26am

9

Dear @stich86

nothing to do.. it still boot in USB mode instead of PCIe..

so probably this sample has some hardware restriction…

silvia

August 27, 2025, 8:46am

11

Dear @stich86

stich86

September 18, 2025, 7:40pm

12

HI @silvia

looks like the module is working in PCIe-RC mode.. but not EP.

Anyway, i’m trying to use this module in RC mode, but as it stuck in R11 branch, the r8125 kernel module doesn’t have IPA offload, so the module cannot go over 250mbps.

Do you have newer firmware or something that enables IPA offload for r8125 module?

Thanks

silvia

September 22, 2025, 6:17am

13

Dear @stich86