# **EC25** Reference Design

## **LTE Module Series**

Rev. EC25\_Reference\_Design\_Rev.G

Date: 2018-02-09

Status: Released

www.quectel.com

## Our aim is to provide customers with timely and comprehensive service. For any assistance, please contact our company headquarters:

## **Quectel Wireless Solutions Co., Ltd.**

7<sup>th</sup> Floor, Hongye Building, No.1801 Hongmei Road, Xuhui District, Shanghai 200233, China Tel: +86 21 5108 6236 Email: info@guectel.com

### Or our local office. For more information, please visit:

http://quectel.com/support/sales.htm

### For technical support, or to report documentation errors, please visit:

http://quectel.com/support/technical.htm Or Email to: <u>support@quectel.com</u>

#### **GENERAL NOTES**

QUECTEL OFFERS THE INFORMATION AS A SERVICE TO ITS CUSTOMERS. THE INFORMATION PROVIDED IS BASED UPON CUSTOMERS' REQUIREMENTS. QUECTEL MAKES EVERY EFFORT TO ENSURE THE QUALITY OF THE INFORMATION IT MAKES AVAILABLE. QUECTEL DOES NOT MAKE ANY WARRANTY AS TO THE INFORMATION CONTAINED HEREIN, AND DOES NOT ACCEPT ANY LIABILITY FOR ANY INJURY, LOSS OR DAMAGE OF ANY KIND INCURRED BY USE OF OR RELIANCE UPON THE INFORMATION. ALL INFORMATION SUPPLIED HEREIN IS SUBJECT TO CHANGE WITHOUT PRIOR NOTICE.

## COPYRIGHT

THE INFORMATION CONTAINED HERE IS PROPRIETARY TECHNICAL INFORMATION OF QUECTEL WIRELESS SOLUTIONS CO., LTD. TRANSMITTING, REPRODUCTION, DISSEMINATION AND EDITING OF THIS DOCUMENT AS WELL AS UTILIZATION OF THE CONTENT ARE FORBIDDEN WITHOUT PERMISSION. OFFENDERS WILL BE HELD LIABLE FOR PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT OF A PATENT GRANT OR REGISTRATION OF A UTILITY MODEL OR DESIGN.

Copyright © Quectel Wireless Solutions Co., Ltd. 2018. All rights reserved.

## **About the Document**

## History

| Revision | Date       | Author      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|----------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| А        | 2016-04-01 | Winter CHEN | Initial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| В        | 2016-08-22 | Yeoman CHEN | <ol> <li>Added ADC interface design in Sheet 1</li> <li>Added power supply for codec in Sheet 3</li> <li>Added note for UART Translator (Transis<br/>Solution) in Sheet 4</li> <li>Changed some DGND to AGND in audio design<br/>Sheet 5</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| С        | 2016-10-14 | Eden LIU    | Added the reference design of SGMII and FC20 module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| D        | 2016-11-11 | Power JIN   | <ol> <li>Modified the connection of network name<br/>PCM_IN_BT and PCM_OUT_BT in Sheet 1</li> <li>Added note 7 in Sheet 7</li> <li>Added note 6 in Sheet 9</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| E        | 2017-04-06 | Eden LIU    | <ol> <li>Newly opened pins 37~40 for BT UART, and<br/>removed the multiplexing between Main UART<br/>and BT UART in Sheet 1</li> <li>Newly opened the SD card interface</li> <li>Added the power supply control pin of SD card<br/>interface in Sheet 2</li> <li>Modified network name TXD_MCU as RXD,<br/>RXD_MCU as TXD, CTS_MCU as CTS,<br/>RTS_MCU as RTS, RI_MCU as RI, DCD_MCU as<br/>DCD, DTR_MCU as DTR in Sheet 2 and Sheet 4</li> <li>Modified the power supply circuit for PCM Codec<br/>in Sheet 3</li> <li>R0904 is not mounted because SDIO_CLK in<br/>FC20 is pulled up internally</li> <li>Modified network name PCM_IN_BT as</li> </ol> |  |  |

F

G

|            |          | PCM_OUT_BT, PCM_OUT_BT as PCM_IN_BT in<br>Sheet 1 and Sheet 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |          | <ol> <li>8. Modified the unidirectional off-page connectors of<br/>SDIO_CMD, SDIO_D0, SDIO_D1, SDIO_D2 and<br/>SDIO_D3 to bidirectional ones in Sheet 1 and<br/>Sheet 9</li> <li>9. Removed resistors R912, R913 and added<br/>resistor R0920 in Sheet 9</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

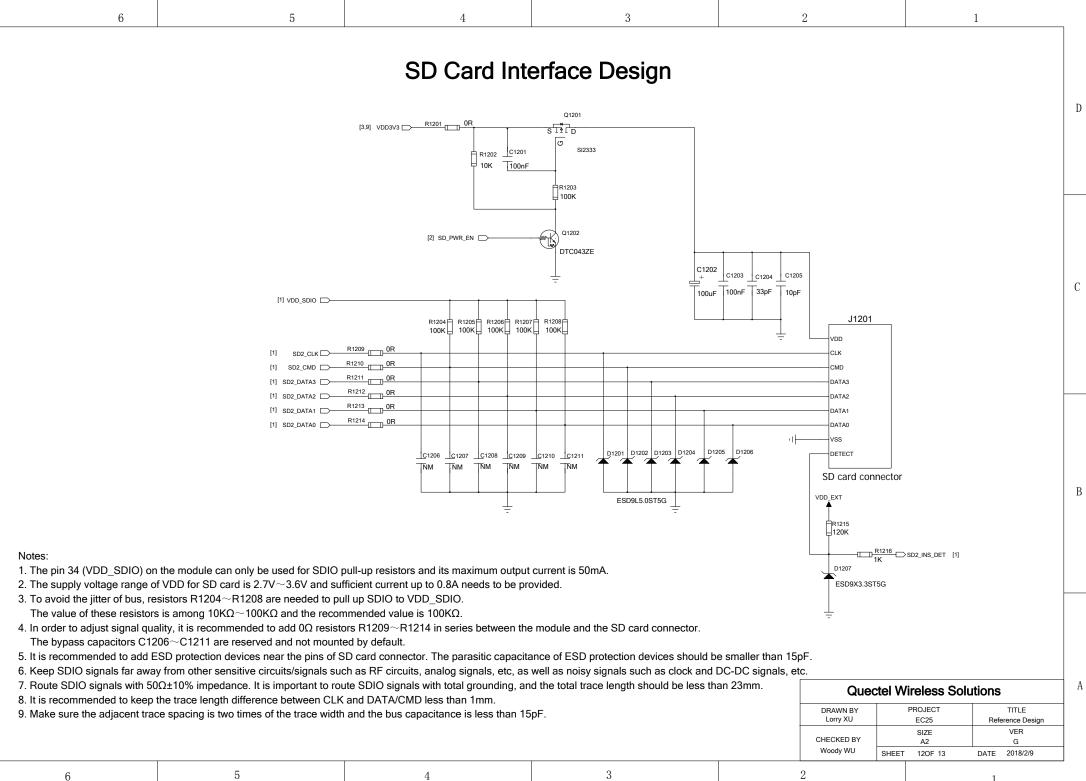

|            |          | 10. Added the reference design for SD card interface in Sheet 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |          | 11. Modified the drive circuit of indicator STATUS in<br>Sheet 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2017-06-15 | Lorry XU | <ol> <li>Modified the names of the pins 28~33 on U0101-A<br/>from SD2_XXX to SDC2_XXX in Sheet 1</li> <li>Modified the unidirectional off-page connectors<br/>TXD and RXD that connect to U0201 in Sheet 2</li> <li>Added resistors R0524, R0525 to pins 17, 20 on<br/>audio codec ALC5616 respectively in Sheet 5 and<br/>added note 2</li> <li>Added Sheet 6 of the reference design for audio<br/>codec TLV32AIC3104 (Optional)</li> <li>Moved the reference design for audio interfaces<br/>(handset and earphone applications) to Sheet 7<br/>and added notes 3~7</li> <li>Renamed the components in Sheets 7~13 (due to<br/>the addition of Sheet 6)</li> <li>Added capacitors C1202, C1204 and C1205 for<br/>SD card interface in Sheet 12 and removed the<br/>previous note 3</li> <li>Added a TVS component D1304 on USB_BOOT<br/>network in Sheet 13</li> </ol> |

|            |          | <ol> <li>Changed R0110 and R0112 to L0101 on the USB differential signals in Sheet 1</li> <li>Added C0201, C0202 and C0203 capacitors on the PWRKEY, WAKEUP_IN_EC25 and W_DISABLE_EC25 signals in Sheet 2</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            |          | <ul><li>W_DISABLE_EC25 signals in Sheet 2</li><li>3. Deleted C0201 capacitor between Q0205 source</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

and gate electrodes in Sheet 2

and 30 pins of U0601 in Sheet 6

to 0R in Sheet 4

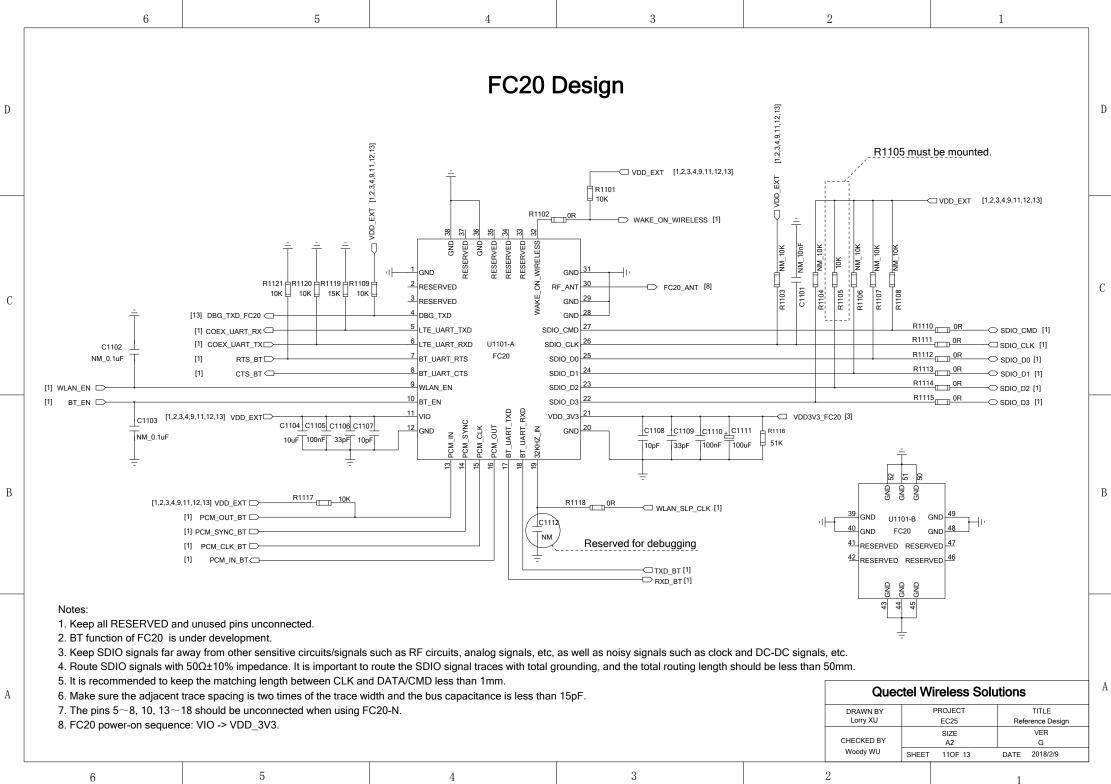

COEX\_UART\_RX,

4. Changed R0407~R0409 resistors value from 22R

5. Added R0618~R0621 0R resistors on 19, 23, 29

6. Added pull-down resistors R1119~R1121 on

COEX\_UART\_TX

2018-02-09

Woody WU

and

RTS\_BT signals in Sheet 11

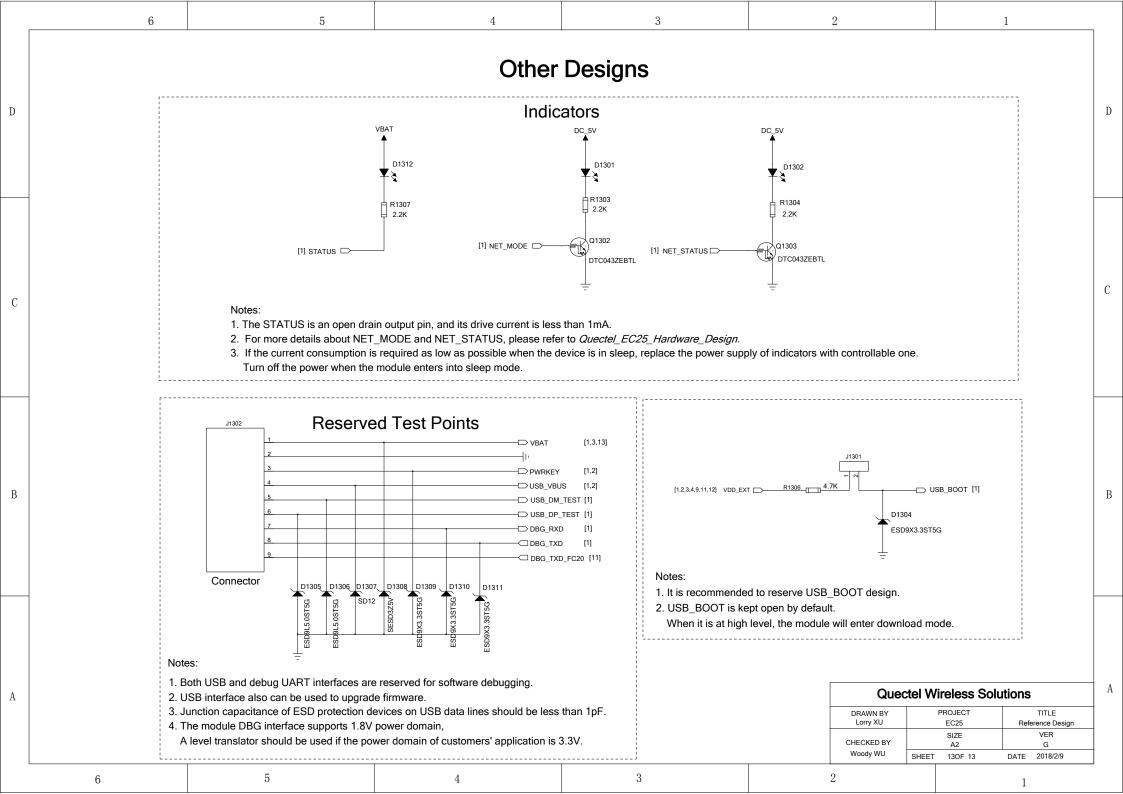

- 7. Changed STATUS reference design in Sheet 13

- 8. Changed R1306 resistance from 10K to 4.7K in Sheet 13

## Contents

| Ab | out the | Pocument     | 2   |

|----|---------|--------------|-----|

| Со | ntents  |              | 5   |

| 1  | Refer   | ence Design  | 6   |

|    |         | Introduction | ~   |

|    | 1.1.    | Introduction | . 6 |

# **1** Reference Design

## 1.1. Introduction

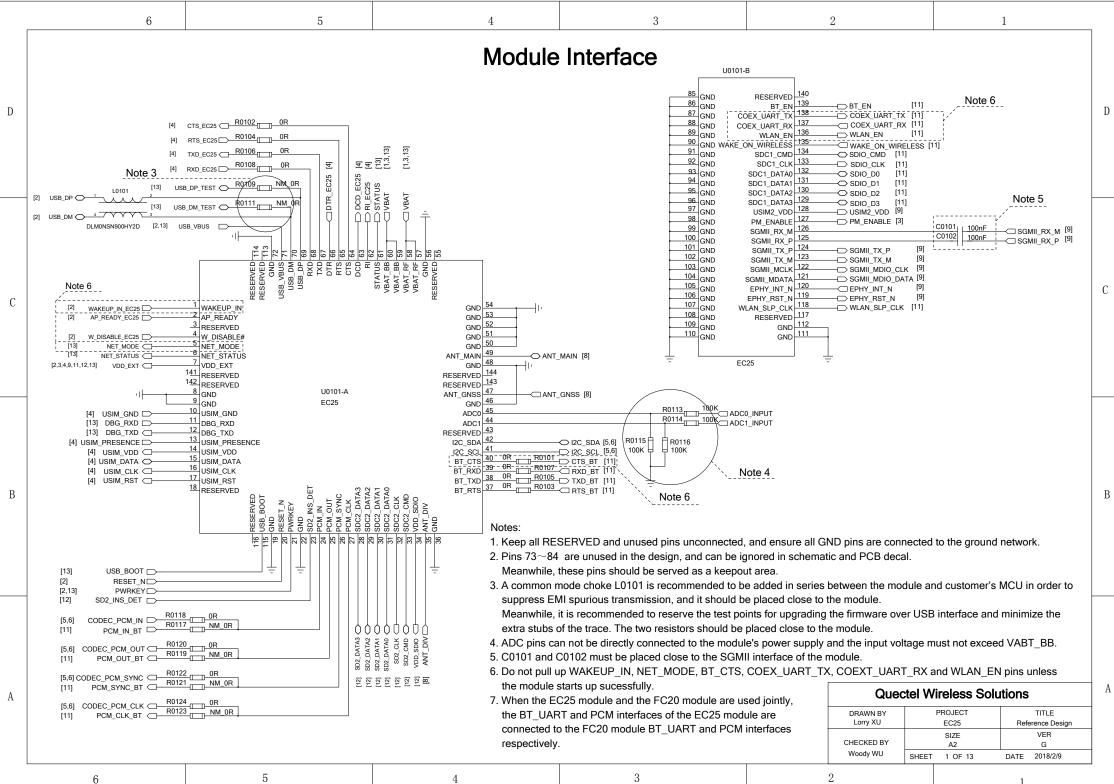

This document provides the reference design for Quectel EC25 module.

## **1.2. Schematics**

The schematics illustrated in the following pages are provided for your reference only.

D

С

В

А

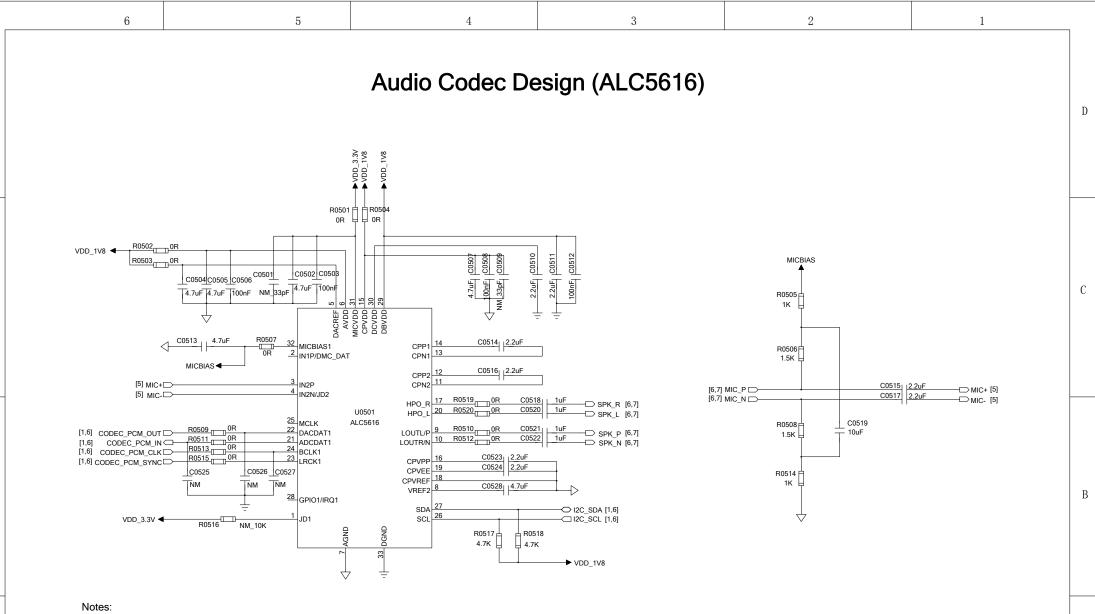

1. ALC5616 power-on sequence: DBVDD/I2C pull-up power/AVDD/DACREF/CPVDD -> MICVDD -> software initialization.

D

С

В

А

2. ALC5616 power-off sequence: close codec function by software-> MICVDD -> DBVDD/I2C pull-up power/AVDD/DACREF/CPVDD.

3. EC25 module will automatically initialize the codec via I2C interface after it is turned on successfully, so all power supplies for the codec need to be powered on before that.

| Lory XU EC25 Reference |          |   |   |   |   | Quectel Wireless Solutions |               | utions                    |

|------------------------|----------|---|---|---|---|----------------------------|---------------|---------------------------|

| CHECKED BY A2 C        |          |   |   |   | - |                            |               | TITLE<br>Reference Design |

| SHEEL 5 OF 13 DATE 201 |          |   |   |   | - |                            |               | VER<br>G                  |

|                        | <u> </u> | F | 4 | 2 |   | )                          | SHEET 5 OF 13 | DATE 2016/2/9             |

А

#### Notes:

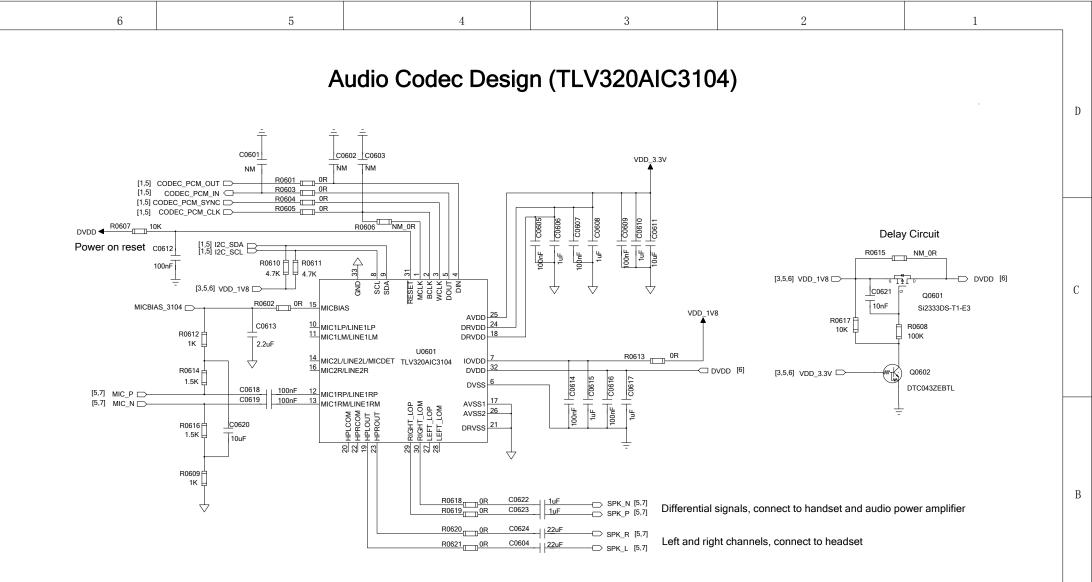

1. TLV320AIC3104 power-on sequence: IOVDD -> AVDD/DRVDD -> DVDD -> software initialization.

4

2. The RC delay circuit, which is assembled with C0621 and R0608, is used to ensure that the power-on time difference between AVDD and DVDD is within 5ms.

3. The RESET pin must be driven at low level for at least 10ns after all power supplies for TLV320AIC3104 are at their specified values.

4. EC25 module will automatically initialize the codec via I2C interface after it is turned on successfully, so all power supplies for the codec need to be powered on before that.

|    | Quectel Wireless Solutions |            |                           |  |

|----|----------------------------|------------|---------------------------|--|

|    | DRAWN BY<br>Lorry XU       |            | TITLE<br>Reference Design |  |

| СН | ECKED BY                   | SIZE<br>A2 | VER<br>G                  |  |

| W  | oody WU SHE                | ET 6 OF 13 | DATE 2018/2/9             |  |

| 2  |                            |            | 1                         |  |

1

6

D

С

В

А

D

С

В

| о <b>Г</b> |   | 0                                     | 0 |   |

|------------|---|---------------------------------------|---|---|

| 6 5        | 4 |                                       | 2 | 1 |

| 0          | 1 | e e e e e e e e e e e e e e e e e e e | - | 1 |

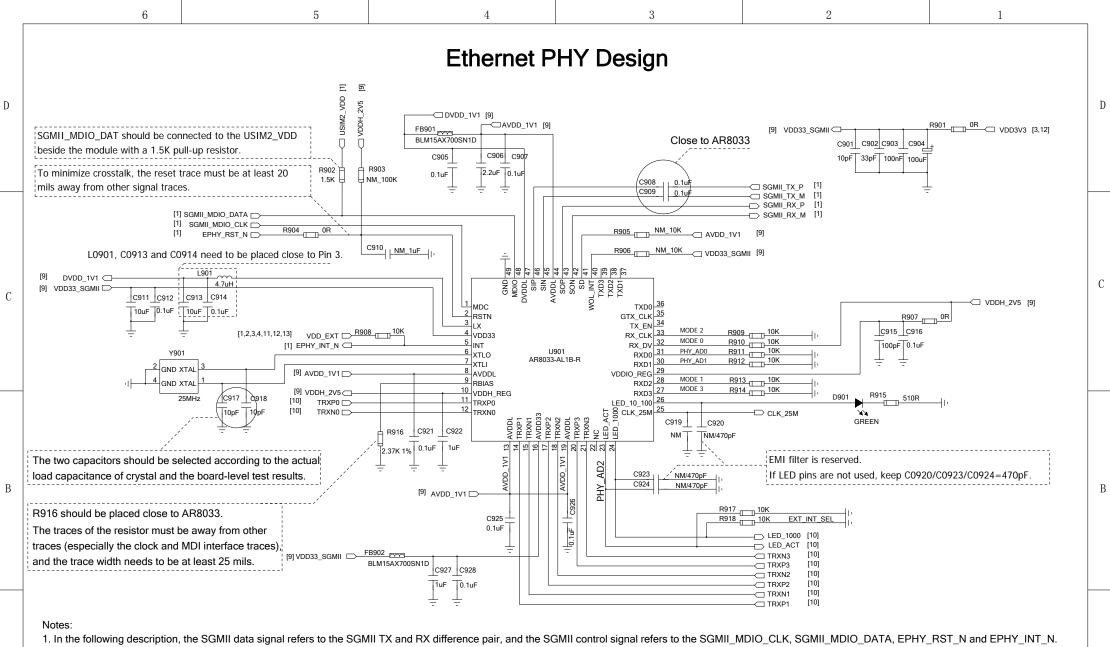

- 2. SGMII data and control signals should be strictly protected with ground and kept away from RF, analog, clock and DCDC signals etc.

- 3. Keep the maximum trace length of SGMII data signal less than 10-inch and keep skew of the TX and RX signals less than 20mil.

- 4. The differential impedance of SGMII data signal is  $100\Omega \pm 10\%$ , and the reference ground of the area should be complete.

| 5. Make sure the trace spacing between SGMII RX and TX is at least 3 times of the trace width, and the same to the adjacent signal traces. |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| 6. The peripheral circuit layout of Ethernet PHY chip AR8033 should be designed on a four-layer PCB,                                       |

|                                                                                                                                            |

and the second layer should be total grounded as the AR8033 reference GND.

А

7. RJ45, network transformer, AR8033, and the SGMII interface should be placed close to each other.

| Quectel Wireless Solutions |               |                  |  |  |  |

|----------------------------|---------------|------------------|--|--|--|

| DRAWN BY                   | PROJECT       | TITLE            |  |  |  |

| Lorry XU                   | EC25          | Reference Design |  |  |  |

|                            | SIZE          | VER              |  |  |  |

| CHECKED BY                 | A2            | G                |  |  |  |

| Woody WU                   | SHEET 9 OF 13 | DATE 2018/2/9    |  |  |  |

|                            |               |                  |  |  |  |

6 5 4 3 2

А

| 6 | 5 | 4 | 3 | 2 | 1 |

|---|---|---|---|---|---|

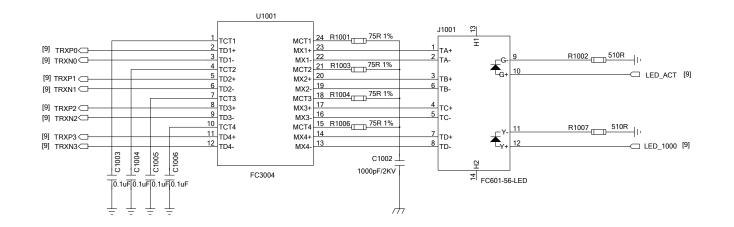

## **Ethernet Network Port Design**

D

С

В

А

| PHY core configuration signal                               | Description                                                   | Default internal<br>weak pull-up/down | Application external<br>weak pull-up/down |  |  |  |

|-------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------|-------------------------------------------|--|--|--|

| PHY_AD2                                                     |                                                               | 1                                     | 0                                         |  |  |  |

| PHY_AD1                                                     | PHY_AD[2:0] set the lower three bits of the physical address. | 0                                     | 0                                         |  |  |  |

| PHY_AD0                                                     | The upper two bits of the physical address are set to 00.     | 0                                     | 0                                         |  |  |  |

| MODE 3                                                      | Mode select bit 3                                             | 0                                     | 0                                         |  |  |  |

| MODE 2                                                      | Mode select bit 2                                             | 0                                     | 0                                         |  |  |  |

| MODE 1                                                      | Mode select bit 1                                             | 0                                     | 0                                         |  |  |  |

| MODE 0                                                      | Mode select bit 0                                             | 0                                     | 1                                         |  |  |  |

| EXT_INT_SEL An external 10K pull-down resistor is required. |                                                               | 1                                     | 0                                         |  |  |  |

| 0 = Pull-down, 1 = Pull-up.                                 |                                                               |                                       |                                           |  |  |  |

#### Notes:

6

D

С

В

А

1. Route MDI differential signals with  $100\Omega \pm 10\%$ , and the reference ground of the area should be complete.

2. Keep skew of the MDI differential signals less than 20mils, and the maximum trace length must be less than 10 inches.

3. To minimize crosstalk, the distance between separate adjacent pairs that are on the same layer must be equal to or larger than 40 mils.

4

| Quectel Wireless Solutions |       |         |      |               |  |

|----------------------------|-------|---------|------|---------------|--|

| DRAWN BY                   |       | PROJECT |      | TITLE         |  |

| Lorry XU                   | EC25  |         | Refe | erence Design |  |

|                            |       | SIZE    |      | VER           |  |

| CHECKED BY                 |       | A2      |      | G             |  |

| Woody WU                   | SHEET | 100F 13 | DATE | 2018/2/9      |  |

|                            |       |         |      |               |  |

1

2

3

D

С

В

А